并行入/串行出移位寄存器执行前面串行入/串行出移位寄存器所做的一切,并同时向所有阶段输入数据。

并行入/串行出移位寄存器存储数据,在一个时钟的基础上移动它,并延迟它的阶段数乘以时钟周期。

此外,并行输入/串行输出实际上意味着我们可以在任何转移开始之前将数据并行加载到所有阶段。

这是一种转换数据的方法平行格式,串行格式。我们所说的并行格式是指数据位同时出现在单独的线路上,如下所示每个数据位对应一个数据位。

通过串行格式,我们的意思是数据位在单个线路或电路上按时间顺序呈现,就像下面的框图上的“数据输出”的情况一样。

下面我们仔细看看一个3级并行输入/串行输出移位寄存器的内部细节。

一个阶段由一个类型组成D.触发器,以及一个与或选择器,以确定数据是并行加载,还是将存储的数据向右移动。

一般来说,根据所需的阶段数,这些元素将被复制。由于空间的限制,我们展示了三个阶段。

真实部件的四个,八个或十六位是正常的。

上面我们展示了当SHIFT/LD '逻辑低时的平行负载路径。上与门为D服务一个D.B.D.C是否启用,将数据传递给类型为D.触发器Q一个问:B.D.C分别。

在下一个正向的时钟边缘,数据将从D到Q的三个FFs时钟。三位数据将载入Q一个问:B.D.C同时。

刚才描述的并行负载的类型,其中的数据负载时钟脉冲被称为同步负载因为数据加载与时钟同步。

这需要与之区分异步加载其中负载由不需要时钟的触发器的预置和清除引脚控制。

在单个设备中只使用其中一种加载方法,同步加载在更新的设备中更常见。

当shift /LD '是高逻辑时,移位路径如上所示。较低的和盖茨对喂养的对或门使能向我们提供SI到D的移位寄存器连接一个,问一个到DB.,问B.到DC,问C所以。在连续的脉冲中,时钟脉冲将导致数据右移。

下面的波形显示了三位数据的并行加载和该数据的串行转换。D at d的并行数据一个D.B.D.C转换为串行数据。

我们之前用单词进行了用于并行装载和转换的单词,现在被设置为上面的波形。

我们举个例子101到并行输入DAA.D.BB.D.CC.。接下来,SHIFT/LD '降低了数据的加载,而不是数据的移动。

由于设置和保持要求,在时钟脉冲之前和之后需要较短的时间。它比必须更宽。

虽然,具有同步逻辑,方便使其宽。我们本可以使活跃的低班次/ ld'差不多两个时钟,低几乎是一个时钟1在t之前回到高处3.。

重要的因素是,它需要低的时钟时间t1使时钟能够并行加载数据。

注意在t点1数据101在维一个D.B.D.C时钟从D到Q的触发器显示在Q一个问:B.问:C在时间t.1。

这是与时钟同步数据的并行加载。

既然数据已加载,我们可能会提供它的转换为换档/ ld'高电平,以便在t之前转换2。

在t2数据0.在问C被移开了那么哪个和Q是一样的呢C波形。它要么移动到另一个集成电路中,或者如果没有任何连接,则丢失。

q的数据B.,一个0.平移到QC。这1在问一个被平移成QB.。与“数据在”a0.,问一个就变成了0.。T.之后2,问一个问:B.问:C=010。

T.之后3.,问一个问:B.问:C=001。这1,最初存在于q一个后t1,现在存在于SO和Q处C。

如果存在,则最后数据位将移出到外部集成电路。T.之后4.并行负载的所有数据都消失了。

在时钟t5.我们展示数据的移入1显示在SI上,串行输入。

问:为什么在换档寄存器上提供SI和所以引脚?

答:这些连接允许我们进入级联移位寄存器级,以提供比单个IC(集成电路)包装中的大移位器。它们还允许与微处理器相同的其他IC的串行连接。

让我们仔细看看作为集成电路的并行输入/串行输出移位寄存器,由Texas Instruments提供。

对于完整的设备数据表,请遵循这些链接。

上面显示的SN74ALS166是与前面并行输入/串行输出移位器数字最接近的实际匹配部分。

让我们注意一下上面图中的微小变化。首先,有8个阶段。我们只展示三个。

所有8个阶段都显示在上面链接的数据表上。制造商标记数据输入A,B,C等到H.

换档/负载控制称为SH / LD'。它从我们以前的术语中缩写,但有效:如果低电平,则平行负载,如果高电平。

移位输入(串行数据输入)是在ALS166上,而不是SI上。时钟CLK是由一个禁止信号CLKINH控制的。

如果CLKINH很高,时钟被抑制或禁用。否则,这个“实部”与我们已经详细讨论过的部分是相同的。

以上是数据表中提供的SN74ALS166的ANSI(美国国家标准协会)符号。

一旦我们知道零件是如何运作的,就可以方便地将细节隐藏在一个符号内。符号有许多一般形式。

ANSI符号的优势在于,标签提供了零件如何操作的提示。

74ASL166顶部的大缺口块是ANSI符号的控制部分。这是一个由R.。

有三种控制信号:M1(转变),平方米(负载),C3 / 1(箭头)(抑制时钟)。这个时钟有两个功能。

首先,C3.用于在任何前缀为3的地方移动并行数据。第二,无论何时M1,如1的C3 / 1(箭头),数据如右侧指向箭头所示移位。

斜杠(/)是这两个功能之间的分隔符。8班级,如标题所示SRG8,由外部输入识别A, B, C,来H。

内部2,3D显示数据,D.,是由平方米[装载]和C3.时钟。在这种情况下,我们可以得出结论,并行数据是与时钟同步加载的C3.。

上一级为一个是否一个比其他块更宽的块来容纳输入塞。

传奇1,3D意味着塞是由M1[转移]和C3.时钟。因此,我们期望在塞当移位而不是平行装载时。

ANSI/IEEE基本门矩形符号以上提供以比较更熟悉形状的象征这样我们就可以破译与之相关的符号的意义CLKINH和CLK前一个ANSI SN74ALS166符号上的引脚。

这CLK和CLKINH喂养一个或门上的SN74ALS166 ANSI符号。或表示由= >在矩形的插图符号上。

输出端的长三角形表示一个时钟。如果有一个带箭头的气泡,这将指示负时钟边缘(从高到低)的移位。

由于没有气泡与时钟箭头,寄存器转移到正(低到高过渡)时钟边缘。

长箭侠,传说之后C3/1指向右侧表示从右移右转,这是符号。

SN74ALS165的部分内部逻辑并联/串行,异步负载移位寄存器从上面的数据表再现。

查看本节开头的链接以获得完整的图表。到目前为止,我们还没有研究数据的异步加载。

首先,加载是通过应用适当的信号到放(预设)和重置(清除)触发器的输入。

上面的与非盖茨喂放插针的FFs和也级联到较低与非门喂重置FF的别针。

较低的与非门将信号从中取值放销的重置销。

首先,SH / LD的必须把低使能上、下与非盖茨。

如果SH / LD的在逻辑上高相反,逆变器提供了一个逻辑低对所有与非盖茨将迫使高出来,释放“活跃低”放和重置所有FFs的引脚。

没有装载FFs的可能性。

与SH / LD的举行低,我们可以源,例如数据1并行输入一个,它在上面转到0与非门输出,设置FF Q一个到一个1。

这0.在放引脚被送入较低的位置与非大门,它倒向a1,释放重置销的问:一个。

因此,一个数据一个= 1套问:一个= 1。由于这些都不需要时钟,所以加载相对于时钟是异步的。

如果我们不能等待时钟来并行加载数据,或者不方便产生单个时钟脉冲,我们就使用异步加载移位寄存器。

提供数据的唯一区别0.并行输入一个它是反转的吗?1出了上门释放放。

这1在放是a的倒立0.在下面的门,拉重置到一个低,重置问:一个= 0。

以上SN74ALS166的ANSI符号有两个内部控制C1.(负载)和C2.时钟的或的函数(clkinh,clk.)。

SRG88-stage移器说。箭头后C2.指示向右或向下移动。塞输入是由内部标签指示的时钟函数二维。

并行数据输入A, B, C来H是一个函数C1.[装载],由内部标签指示1 d。

C1.时宣称sh / LD ' = 0由于在输入端的半箭头逆变器。

将其与先前同步ANSI SN75ALS166的时钟进行控制并行数据输入。注意ANSI数据标签的差异。

在CD4014B上面,M1时宣称LD / SH ' = 0。平方米时宣称LD / SH ' = 1。

钟C3/1用于并行加载数据2,3D当平方米是否如2、3前缀标签。

针P3来P7被理解为内部的内部2、3前缀标签,P2和P8。在塞, 这1、3 d前缀意味着M1和时钟C3.是输入串行数据所必需的。

当M1激活时,右移发生,如所示1在C3/1箭头。

CD4021B是一个类似的部分,除了异步并行加载数据,这意味着没有任何数据2数据标签中的前缀1 d对于引脚P1, P2到P8。

当然,前缀2在标签二维在输入塞上面说数据被输入了这个密码。这或门框显示时钟是由LD / SH '。

以上SN74LS674内部标签分析16表示16位换档寄存器。

这模式标记为符号顶部的控制部分的输入1、2立方米。内部M3是输入的函数吗模式和G1.和G2.如1、2前M3。

底部标签G显示一个和任何这样的函数G输入。输入R / W '内部标签G1/2 EN。

这是一个使能EN.(由G1和G2)用于该符号中其他地方使用的三态器件。

我们注意到,计算机科学的on(引脚1)是内部的G2.。芯片选择计算机科学的也是和用输入edCLK给生物钟C4。

时钟箭头中的气泡表明活动处于负(从高到低的转换)时钟边缘。

斜杠(/)是一个分隔符,表示时钟的两个函数。在削减之前,C4表示对前缀为的任何东西的控制4.。

斜线之后是3 '(箭头所指)表明转移。这3 '的C4/3”当M3不被断言时,意味着移动(模式= 0)。长箭头指示右移(向下)。

从控制部分向下移动到数据部分,我们有外部输入P0-P15(7-11, 13-23)。

前缀3、4内部标签3、4 d表明M3而时钟C4控制并行数据的加载。

这D.代表数据。这个标签被认为适用于所有的并行输入,尽管没有显式地写出来。

找到标签3 ', 4 d在右边P0(pin7)阶段。补充,3.表明M3 =模式= 0输入(班次)SER / Q15(pin5)在时钟时间,(pin5)4.3′,4D)对应于时钟C4。

换句话说,with模式= 0,我们将数据转移到问:0.从串行输入(引脚6)。所有其他阶段在时钟时间右移(下)。

移动到符号的底部,向右指向的三角形表示两者之间有一个缓冲区问:和输出引脚。

向下的三角形表示一个三态器件。我们前面说过三态是由enable控制的EN.,实际上G1和G2从控制部分。

如果R / W = 0,三态系统被禁用,我们可以把数据转换成问:0.通过塞(pin 6),上面我们忽略了一个细节。我们真正需要的模式= 0,R / W = 0 = 0, CS

SN74LS674的内部逻辑和总结控制信号操作的表格可以在部分顶部的项目符号列表中的链接中找到。

如果R / W ' = 1,三态状态已启用,问:15转变了SER / Q15(引脚6)和再循环到问:0.舞台通过右手线到3 ', 4 d。

我们假设CS '是低的,因此时钟C4/3 '和G2EN.可以停课。

并行入/串行出移位寄存器的一个应用是将数据读入微处理器。

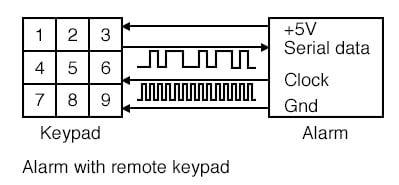

上面的警报是由一个远程键盘控制的。报警箱提供+5V并接地到远程键盘电源。

警报器每隔几十毫秒读取远程键盘通过发送移位时钟到键盘返回串行数据显示通过并行进/串行出移位寄存器的键的状态。

因此,我们读到有四根电线的九个按键开关。如果我们要为这9个键中的每一个都运行一个电路,需要多少根电线?

平行/串出移位寄存器的实际应用是只需几个引脚就将许多开关闭合到微处理器上。

一些低端微处理器在8针封装上只有6-I/O(输入/输出)管脚。

或者,我们可能已经使用了84针封装上的大部分针。我们可能想要减少线路板、机器、车辆或建筑物周围的电线数量。

这将增加我们系统的可靠性。据报道,那些减少汽车上电线数量的制造商生产出了更可靠的产品。

在任何情况下,只需要三个微处理器引脚,以从上图中的交换机中的8位数据中读取8位数据。

我们选择了异步加载设备CD4021B,因为它更容易控制数据的加载,而不必生成单个并行加载时钟。

移位寄存器的并行数据输入被拉到+5V,每个输入端都有一个电阻。

如果所有交换机都打开,所有1当微处理器移动时,s将被装入移位寄存器LD / SH '从低到高的线,然后在预期移位时返回低电平。

任何开关闭包都将应用逻辑0.s对应的并行输入。函数将并行加载P1-P7上的数据模式LD / SH ' = 1由微处理器软件生成。

微处理器产生移位脉冲并为每个8位读取一个数据位。

这个过程可以完全通过软件来完成,或者更大的微处理器可以有一个或多个串行接口来用硬件更快地完成任务。

与LD / SH ' = 0,微处理器产生0.来1过渡的移位时钟线,然后读取数据位串行数据线。这对所有8位都是重复的。

这塞如果需要读取更多的开关触点,移位寄存器的一行可以由另一个相同的CD4021B电路驱动。

在这种情况下,微处理器产生16个移位脉冲。更有可能,它将由与此串行数据格式兼容的其他东西驱动,例如,模数转换器,温度传感器,键盘扫描仪,串行只读存储器。

至于开关闭合,它们可能是机器托架上的限位开关、超温传感器、磁簧开关、门窗开关、空气或水压力开关、固态光开关。

相关工作表: