选择正确的赶回作为PCIe协议或重新定时设备扩展信号范围

2021年1月12日通过Tam,微芯片赶回或重新定时设备可以扩展外围组件接口表达(作为PCIe®)协议的信号范围。本文讨论了如何选择最好的一个计算系统和NVMe™存储应用程序的今天和未来。

高性能云计算系统的数据速率要求继续推进并创建一个重要的信号完整性挑战各种各样的组件部署在数据中beplay体育app 苹果心设备。数据速率的增加导致信号传输距离和减少可以限制系统的可伸缩性。而赶回或重新定时设备可以帮助解决这种限制,各有优点和缺点。

本文描述了这些设备可以扩展外围组件接口表达(作为PCIe®)协议的信号范围,以及如何选择最好的一个计算系统和NVMe™存储应用程序。

作为PCIe信号完整性的挑战

作为PCIe接口标准是一个最受欢迎的接口用于今天的高性能计算系统和数据中心。作为PCIe的数据率已经从第一代(Gen1) 2.5 gt / s第五代(Gen5) 32吨/ s。第六代6 (Gen6)将再次以前版本的数据率的两倍。随着频率增加到支持更高的数据率,保持足够的信号完整性在一个合理的系统成本已经成为一个挑战。赶回和调整时间的设备都可以帮助弥合差距的解决方案。

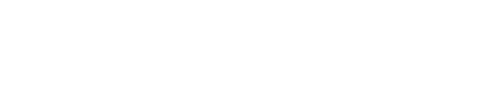

FR4多氯联苯是最受欢迎的和具有成本效益的材料在电子工业。FR4 PCB材料表现良好在相对较低的频率衰减可以接受低于10 ghz。随着数据速率的增加,然而,FR4材料频率响应降低。

Megtron 6等PCB材料有更好的频率响应和经验较少的信号损失,但代价巨大的溢价。例如,Megtron 6 FR4成本的7倍左右。其他材料在微波频率范围内可以有更高的成本的溢价。下面的方程近似信号丢失在dB /英寸由于跟踪损耗和介电损耗。

.jpg)

地点:

- W =跟踪宽度mil,假设5毫升计算

- F = GHz频率

- Df =耗散因子或损耗角正切(依赖于PCB材料)

- Dk =介电常数(依赖于PCB材料)

图1显示了一个阴谋的PCB衰减FR4和Megtron 6 PCB材料。根据复杂性和PCB的大小,搬到一个高质量的材料成本PCB的成本可能是高昂的。

图1所示。衰减与频率的函数PCB材料

一些应用程序可能需要连接器提供信号设计的其他部分如背板和场外的插件卡片。连接器是一个额外的因素信号损失。作为PCIe杰姆连接器增加约1.5 db损失32 gbps。作为PCIe Gen5标准规定一个容许频道损失预算是36分贝。

使用赶回或调整时间作为PCIe信号可以帮助保持完整性。做出正确的选择需要一个基本的了解两者之间的差异。

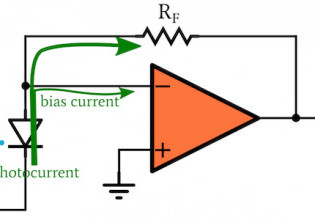

赶回来解释

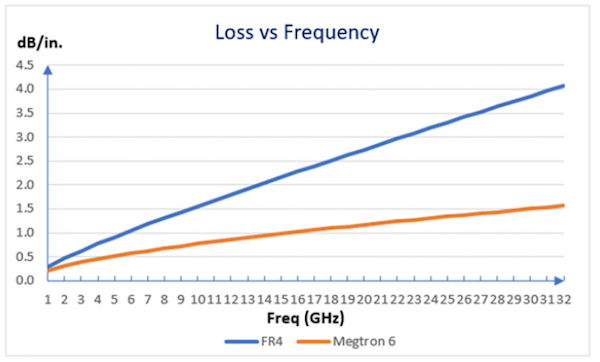

赶回是一个高带宽放大器和接收(RX)均衡器(EQ)来弥补由于PCB的痕迹或电缆衰减频率相关。连续时间均衡器(CTLE)的主要功能是打开封闭的扭曲的波形。传输(TX)方面可以包括一个预加重函数(传递均衡器)拉弯以使传输波形。

串行接口的信号完整性等显示接口,USB,雷电,HDMI,作为PCIe可以受益于它的路径将赶回如果跟踪或电缆长度超出标准范围。模拟放大器不区分任何特定的协议标准,因为它没有链接培训过程。因为它是协议无关,链接可以成为任何接口标准不一致。它不需要一个时钟,因为它自然模拟电路。

赶回的主要缺点是,它不仅放大了数据信号,而且放大任何噪声在信号路径。放大器的噪声地板本身和可以添加自己的噪音的整体噪声图信号。典型的线性赶回均衡器添加8 ps的固有抖动信号,并对国际米兰的象征(ISI)抖动干扰。赶回不能弥补non-ISI抖动。相比,调整时间,赶回,在某些情况下,更低的能耗和总成本。一个典型的赶回延迟大约是100 ps。

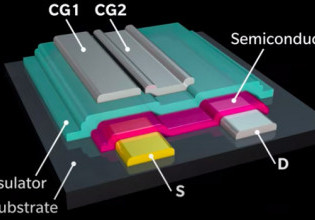

图2概述了模拟单巷赶回的关键构件。

图2。单行道赶回框图

赶回的高带宽放大器可以是线性或限制(非线性)。线性放大器可能提供一些伪链接作为PCIe协议培训功能,根据设计实现。限幅放大器不支持任何类型的链接训练序列的任何协议。限幅放大器只支持两个阈值水平来确定接收信号的条件。因为大多数链接培训脉冲需要中间阈值的检测,是非常困难的赶回来支持训练序列。这是限幅放大器的“盲点”。

Redrivers也是有限制的

Redrivers作为PCIe创一创3可以支持数据速率当应用程序是足够小和有限的复杂性提高信号传输距离。然而,随着设计规模和复杂性的增加,赶回再也不能补偿信号损失,同时仍然使用具有成本效益的材料。级联两个redrivers克服问题是不实际的。任何噪音或随机抖动会放大以及所需的信号。模拟放大器不能重置任何噪音或时间预算。因此,级联两个redrivers会噪音的数据量的两倍。

16岁作为PCIe创4 gbps数据速率构成一个更大的挑战来自信号完整性的观点。大多数作为PCIe创4接口应用程序在云存储,服务器和高性能计算平台,16 gbps的链接在哪里需要驱动长痕迹,连接器,电缆槽,插件卡(aic)。赶回只是不使用这些数据在数据中心基础设施的用例。

作为PCIe 5.0的发布在2019年撞32 gbps的数据速率。高端网络系统利用400 gbps以太网,多- 200 gbps InfiniBand和加速器/ GPU组件和技术部署的主要驱动因素是不断增长的利率作为PCIe链接。NVMe SSD组件部署在企业服务器和存储系统是另一个司机为这些更高的数据速率。其他串行协议USB4.0,显示端口2.0,和迅雷3.0也翻倍数据速率。

调整时间的救援

考虑到需要解决这些高速信号完整性问题,作为PCIe标准,作为PCIe创4,开始定义作为PCIe调整时间的要求。标准定义了一个重新定时物理层协议组件”意识到,必须与任何一对组件互操作与任何兼容的通道两侧的调整时间。“Retimers有更高程度的复杂性比赶回。4.3节作为PCIe作为PCIe创创4和5的详细规格覆盖了调整时间要求。

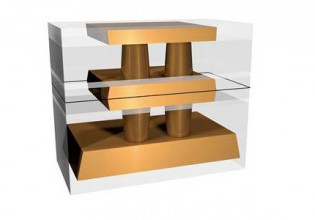

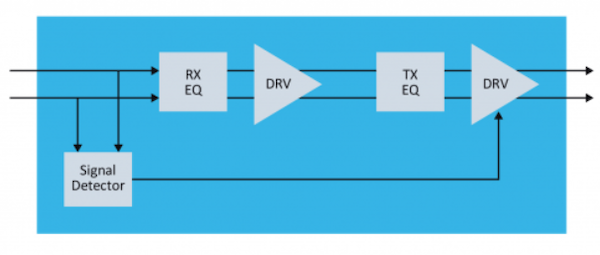

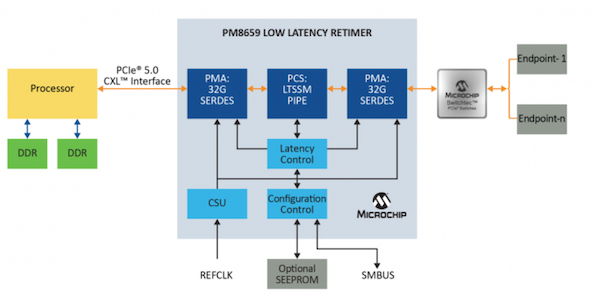

图3展示了一个车道双向调整时间的高级框图。

图3。调整时间框图

作为PCIe标准指的是这是一个作为PCIe x1配置。大多数作为PCIe retimers x4(8总道:4 RX和4 TX),乘以8(16通道)或x16(32通道)。

物理层是物理媒介附件(PMA:物理区块)的序列化器/部分(并行转换器),接收和传输数据。PMA是混合信号构建块。在接收端,扭曲的信号是平衡的使用CTLE和噪声过滤。

的心重新定时时钟和数据恢复(CDR)块。CDR复苏中的嵌入式时钟与数据并行领域。PMA块并行数据传输序列化和反序列化数据的物理编码子层(pc)。

眼睛监视模块生成的波形实时捕捉接收眼模式用于调试目的。电脑处理链接训练状态状态机(LTSSM)和管(PHY接口作为PCIe)功能。电脑是一个纯粹的数字部分。

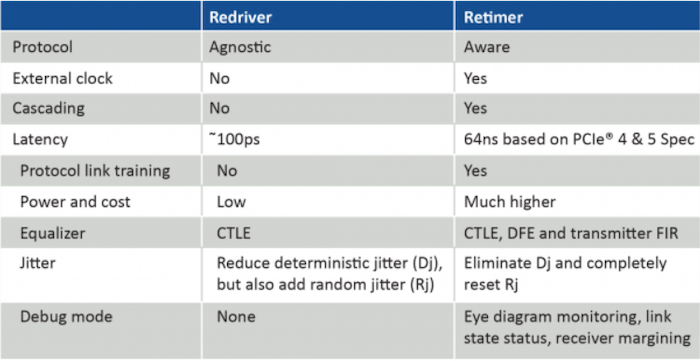

表1总结了赶回之间的关键差异和调整时间。

表1。赶回和调整时间比较

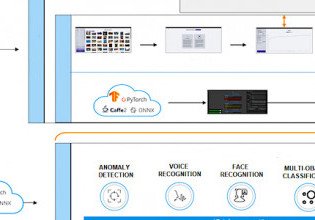

Retimers作为PCIe应用程序的例子

作为PCIe标准是主要的接口标准用于组件部署在数据中心存储、服务器和网络基础设施。作为PCIe接口提供cpu利用高速I / O作为PCIe根事务作为一个复杂的附加SSD驱动器或其他端点组件。图4说明了拓扑从CPU这些端点为例。作为PCIe开关提供了额外的扇出支持更多的端点的目的地。Retimers现在所需的组件支持信号扩展CPU板,底板,电缆,和插件卡。

图4。服务器的例子作为PCIe调整时间

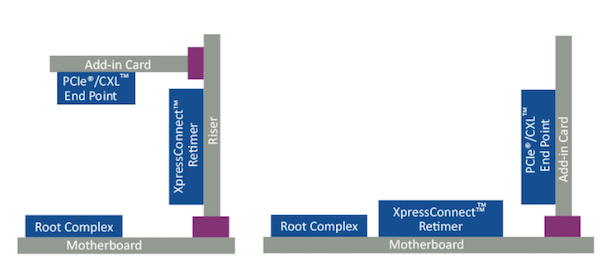

此外,作为PCIe retimers往往用来支持信号调节当电缆和/或多个连接器在数据路径。Retimers常常利用CPU和端点之间下面列出,如图5所示:

- CPU < -调整时间- >插件卡(AIC)

- CPU < -调整时间- > - > AIC立管卡

- CPU < -调整时间- >电缆- > - > AIC切换

- CPU < -调整时间- >电缆- >另类投资会议

图5。调整时间在立管卡AIC重新定时AIC主板

Redrivers retimers有助于保持信号完整性在许多数据中心系统的应用程序。根据设备的复杂性和数据率设计、redrivers可以用于更小的系统,操作较低数据率。

数据率高于16 gbps, redrivers没有足够的能力来弥补退化的重要信号。作为PCIe 4.0和5.0,需要使用retimers合规运作。其他串行协议,如USB 4.0和迅雷3.0还指定调整时间需求的角度规范。

因为retimers重置信号抖动的预算和再生一个肉干净的信号传输,没有插入损耗和设计师可以实现计算系统的性能优势和NVMe™存储应用程序在一个合理的系统成本。

引用

- 高速串行总线中继器底漆(PDF)

- 一种总线标准团体®beplay网页版本教育研讨会系列2019(PDF)

- 766:英特尔®Stratix®10设备,高速信号界面布局设计准则(PDF)

- PCI Express基础规范修订5.0 1.0版,2019年

文章内容的一种形式,允许行业合作伙伴分享有用的新闻,信息,技术和关于电路的读者的方式编辑内容并不适合。所有行业的文章受到严格的编辑指南的目的是提供读者有用的消息,技术专长,或故事。在行业的文章中表达的观点和意见不一定是合作伙伴和所有的电路或其作家。