在极态SOC上运行硬实时应用和Linux

2019年3月26日通过蒂姆•莫林微芯片本文讨论了针对PolarFire SoC的基于risc - v的SoC FPGA架构,该架构允许硬实时应用程序和Linux应用程序共存。

本文讨论了针对PolarFire SoC的基于risc - v的SoC FPGA架构,该架构允许硬实时应用程序和Linux应用程序共存。

实时Linux是抢眼,但它究竟是什么意思?实时系统的定义,其最简单的形式是定期执行的。确定主义是对实时系统的第一个订单要求,因为它们通常是控制机器。您不希望在星期二在10毫秒(MS)中从点A到P点B从点A移动到Point B,并在周三在20毫秒内执行相同的操作。同样,飞行员的飞行控制系统应在所有条件下控制飞行表面完全相同的方式。

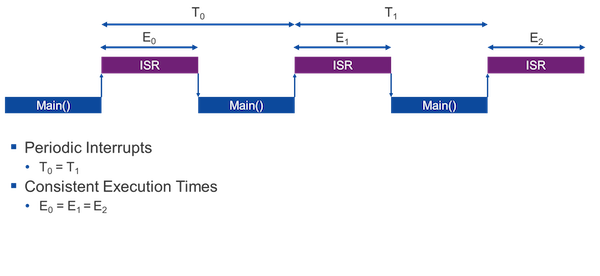

图1示出了确定性系统。定期中断火灾和中断服务程序处理时间关键代码。该代码的执行时间必须是确定性的,以免您最终使用行为的系统,如图2所示,其中硬件发生更新。

图1所示。确定性执行的示例

图2。可变中断服务例程(ISR)执行时间

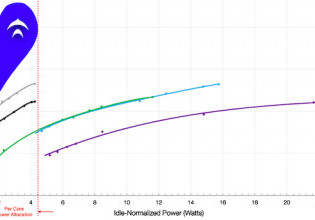

还需要将丰富的Linux和所有相关的中间件带到硬件控制系统中。Linux需要一个内存管理单元(MMU)来为应用程序开发人员虚拟化物理内存。嵌入MMU的处理器也至少包含L1缓存,在大多数情况下是L2缓存。如图3所示,缓存和确定性是相互正交的。在这里,我们可以看到L1或L2 miss会在缓存线被填满时,通过延迟执行管道来引入执行抖动。较大的缓存可以减少缓存丢失的频率,但不能完全删除它们。

图3。L1和L2缓存丢失会影响确定性

在可以运行Linux的处理器中,附加的执行jitter是分支预测器。处理器内核包括分支预测器,以提高应用程序级性能。无论实现如何,都会预测分支机构,有时会错过。

发生小姐发生时,管道会刷新。未命中导致非确定性执行行为。在中断服务例程(ISR)期间,预测器中使用的分支历史表具有主要应用程序代码的执行历史的分支的历史,而不是ISR本身的执行历史记录。这将导致管道在ISR内刷新,导致来自ISR到ISR的可变执行时间。

使用允许用户禁用分支预测器的处理器使应用程序开发人员控制在系统中应用确定主义的应用程序。对于应用范围的确定性,您可以完全禁用分支预测器。当然,分支预测因子就可以提高性能,因此关闭它们会降低性能。

RISC-V PolarFire SoC FPGA架构

有些处理器可以运行Linux,但不能确定地执行代码;有些处理器可以确定地执行代码,但不能运行Linux。在您的嵌入式工具包中有一个能够同时支持这两种方法的架构不是很好吗?微芯片公司最近宣布了一项基于RISC-V的SOC FPGA架构,用于偏光极焦SOC它执行这个任务。

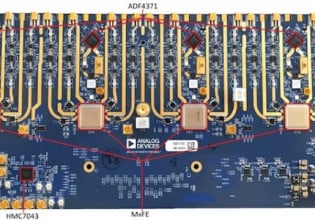

图4包含了四个能够运行Linux的64位RV64GC RISC-V核心,以及无法运行Linux的一个核心(RV64imac)。换句话说,RV64imac不包含MMU,四个RV64GC核心确实包含MMU。

图4。PolarFire SoC架构

RV64IMAC和RV64GC之间的指令集差异很简单;RV64GC包含一个双精度浮点单元。为了提高体系结构中的确定性级别,用户可以在任何内核中关闭分支预测器,无论是在通电后还是在ISR期间。此外,所有五个核心都选择了顺序管道,以增加确定性,并避免对无序机器的Spectre和Meltdown攻击。

到目前为止,我们只讨论了与CPU核心相关的决定歧视。代码需要从内存中执行,因此让我们讨论偏光极焦SOC中的内存子系统。首先,偏光极焦SOC中的整个内存空间是连贯的。

一致性被定义为具有一致性管理器管理多个数据副本的任何存储器,以及只包含单个数据副本的任何存储器都是由它们非常同义的,因为内存层次结构中没有存在其他副本。PolarFire SoC有三个存储器子系统:L1,L2和L3。L3存储器子系统集成了硬化的LPDDR3 / LPDDR4和DDR3 / DDR4 36位控制器。额外的4位用于将其添加到外部L3存储器子系统。

L1内存子系统

四个RV64GC应用程序核心每个都有一个8路组关联,32 kB i $ tims和8路集合,32 kB d $ tim。I $等同于指令缓存,TIM表示紧密集成的内存(TIM)。

I$TIM和D$TIM都是用户可配置的,要求I$TIM和D$TIM必须总是有一种缓存方式。RV64IMAC显示器核心有一个16 KB的双向集关联I$TIM和一个8 KB的DTIM。DTIM是一个可以执行代码的数据暂存存储器。所有L1 TIM功能提供低延迟确定性访问,并具有单错误纠正双错误检测(SECDED)能力。

L2内存子系统

L2存储器子系统的大小为2 MB,具有Secded功能,可以配置为三种不同的模式。一个16路组关联高速缓存,松散集成的内存(LIM)和暂存器内存。LIM存储器可以固定到处理器,并且可以以缓存方式大小 - 换句话说,LIMS可以以128KB块(方式)构造并分配给处理器的独占访问权限。

被配置为LIM,L2存储器子系统提供对其被固定到并相干的核心的确定性访问,因为没有与L1和L3存储器子系统共享其他副本。LIM适用于主要应用程序和ISR中的确定性代码执行。图5示出了当L2存储器子系统被配置为LIM时的确定性系统,并且L1配置为TIM。

图5。用lims和tims确定确定性执行

不幸的是,由于分支预测器的错误预测,即使L2被配置为LIM, ISR执行时间的可变性仍然存在。图6显示了当L1被配置为TIM而L2被配置为LIM时执行的应用程序。横轴表示中断,垂直访问表示ISR中的周期时间。如您所见,随着时间的推移,ISR的执行会发生变化。

图6。分支预测对决定论的影响

图7给出了关闭分支预测器所追求的决定论。

图7。确定性行为

与LIM类似,scratchpad内存可以配置为128 KB的块(方式),并分配给CPU内核。暂存内存作为执行来自LIM的代码的处理器和执行来自L1/L2和L3内存子系统(通常是Linux)的处理器之间的共享内存资源可以很好地工作。如果RV64IMAC应用程序将数据写入scratchpad,并且L1/L2/L3内存子系统中存在该内存位置的副本,那么一致性管理器将保证一致性。通过这种方式,实时应用程序可以与Linux上运行在用户空间中的应用程序一致地共享数据。

图8是偏振光SOC微处理器子系统的一种可能配置。在此配置中,RV64IMAC在RV64GCS运行Linux时提供实时函数。如果您的实时函数需要浮点性能,则RV64GC可以用于该目的,因为可以关闭分支预测器,并且L1存储器子系统可以配置为蒂姆。

图8。连贯的消息传递

PolarFire SoC允许硬实时和Linux应用程序共存

确定性是实时系统的关键要求。然而,市场上有许多处理器可以运行Linux,但不能确定地执行代码,还有一些处理器可以确定地执行代码,但不能运行Linux。PolarFire SoC具有独特、灵活的内存子系统,使硬实时应用程序和Linux应用程序以灵活、一致的方式共存。

行业文章是一种内容的形式,允许行业合作伙伴分享有用的新闻,消息和技术,所有关于电路读者的行为编辑内容并不适合。所有行业文章都受到严格的编辑准则,目的是提供读者有用的新闻,技术专业知识或故事。在行业文章中表达的观点和意见是合作伙伴的观点,不一定是关于电路或其作家的所有人。