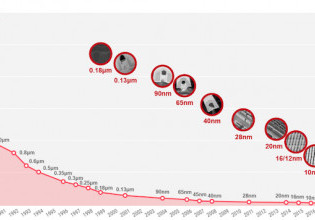

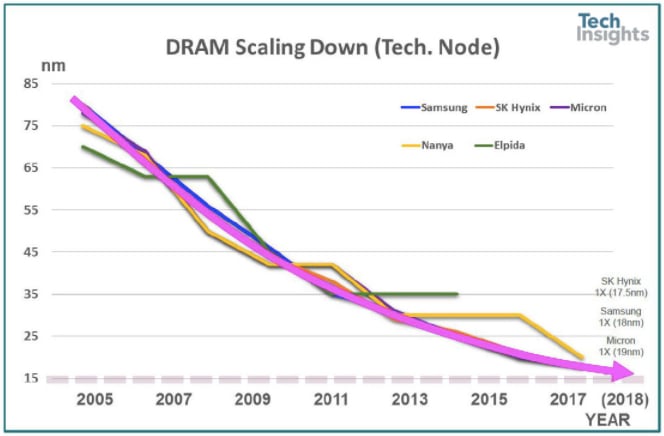

DRAM一直比其他许多其他硅对手缩短。虽然微处理器一直生产到5nm节点,但DRAM仍然停留在20nm和10nm节点之间,大约从2016年开始。理论上,10nm是DRAM的极限。

DRAM缩放趋势达到2018年。使用的图片礼貌科技的见解

因此,制造商创建了一种新的过程节点命名方案,其指内存单元阵列中的活动区域的间距的一半的尺寸。“公约”如下:

- 1x nm.:19nm-17nm(Gen1)

- 1Y NM.:16nm-14nm(Gen 2)

- 1Z NM.: 13nm-11nm(第3代)

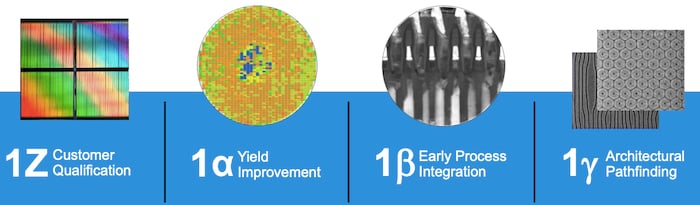

到目前为止,制造商只到达了1z“节点”。现在,Micron Technologies已成为第一家将下一个最小的Diminsion DRAM,1α到市场的公司。

电容长宽比和DRAM缩放

缩放DRAM的众多原因并未像缩放微处理器一样简单(如果您认为这是一个直接的过程)。

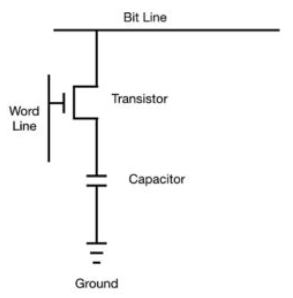

单个DRAM单元由PASS晶体管和存储电容器组成。使用的图像礼貌块和文件

其中一个原因与DRAM的本质有关;它需要一个存储电容来保存数值。由于设备的电容与其物理尺寸直接相关,从侧面缩小电容会降低其效率。不仅电容器不再能够容纳可测量的电荷,而且它还将更快地泄漏电荷,需要更多的动态刷新。

一些行业供应商认为,有必要对材料的重大发展充分克服这一挑战。

制造挑战和DRAM缩放

硅处理通常依赖于光刻以蚀刻到半导体中的详细图案。DRAM电池的光刻设计要求,特别是电容器的复杂性,使制造过程非常困难。

Micron的DRAM路线图继续展开。使用的图像礼貌微米

随着特色收缩,光刻受限于瑞利判据。这一标准指出,用光刻法蚀刻不到所用光波长一半的特征是不可能的。这意味着,当特征蚀刻得足够小时,使用传统技术几乎不可能创造出足够精确的DRAM单元。

一些挑战包括用良好的对准和具有准确纵横比的电容器来图案化电容器孔,以获得可预测行为。

Micron引入了一个新的内存过程节点

虽然这些挑战取得了惊人的缓慢,但一些供应商仍在取得进展。Micron是第一家在最近取得重大进展的公司,昨天成为第一家将1α流程节点带到批量生产的公司。

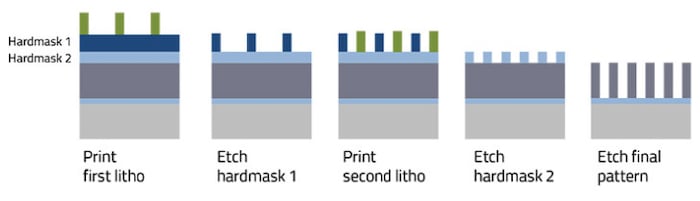

与一些正在寻找极端紫外线(EUV)光刻作为解决方案的公司不同,Micron通过“多重图案”来实现缩小。这种技术背后的想法是通过添加非光刻步骤来提高分辨率来创建单个较大的特征之外的多个小功能。

多个图案化过程。使用的图像礼貌林研究所

Micron的工程师Thy Tran解释道:“我们做了相当简单的工作,基本的想法是用台阶来创造祭祀特征,在这些特征的侧面涂上不同的材料,然后去掉原始的祭祀特征。Voila-two半尺寸功能!重复这个过程,我们得到了1α所需尺寸的四个特征。”

内存密度的40%凹凸

这一消息在内存空间方面意义重大,考虑到微米的新1α DRAM比之前的1z DRAM节点的内存密度提高了40%。美光还声称,与1z移动DRAM相比,新技术可节省高达15%的电能。

据该公司称,今年,1α节点将分发其DRAM产品组合,以支持今天使用DRAM的所有环境。