STMicroelectronics将UVLO(欠压锁定)带到SiC FET

2021年3月26日经过杰克赫兹在设计电路时,特别是在高压应用中,安全性是一个主要问题。新的孤立门驾驶员将欠压安全功能带到SiC FET。

在决定使用哪些组件时,对其偏置条件的彻底了解是至关重要的,这不仅对设计的正常功能,而且对防止任何安全问题也是如此。

设计师可能遇到的一个主要考虑是使用碳化硅(SiC)还是硅(Si)。虽然在许多情况下SiC和Si可以被认为是相同的,但它们在操作上有根本的不同。具体来说,a的I-V曲线SIC FET.与A-Si FET不同的趋势,如果没有正确偏见,留下了不正确的操作和潜在的安全危险的空间。

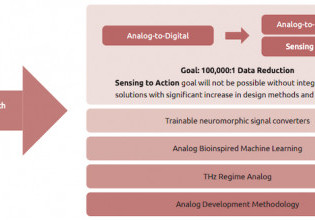

电路块性能因输入电压而异。使用的图像礼貌德州仪器

但是,在实际应用中,偏见永远不可能精确。这种缺陷是由于电流或寄生引起的电源或电池电压的波动引起的。具体措施可以确保SiC场效应管在动态和不可预知的使用情况下的安全运行。

为了更好地理解SiC和Si之间的那些基本区别,有必要看看它们的操作区域。

SiC与Si操作区域

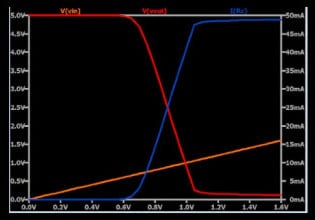

sic和siMosfets.然而,有类似的表现,它们的确切操作行为并不相同当涉及到他们各自电流-电压曲线。

在SI MOSFET中,我D.(排水电流)与vDS.(漏极 - 源电压)曲线最初彼此靠近,然后开始分离和饱和,根据V的不同GS.(gate-source电压)。理论上,假设所提出器件的栅极电压过低。

在这种情况下,该装置在较低电流水平下饱和,导致从设备的极高导通损耗未完全打开但经历高V vDS.价值观。

SiC(左)和Si(右)的I-V曲线。使用的图像礼貌德州仪器

在SIC MOSFET中,观察到相同的趋势;然而,差异是操作区域对栅极电压具有更大的依赖性。如上所述所见,根据栅极电压,SiC FET倾向于在更低的电流下饱和。这种饱和度使得该装置比Si FET更容易受到高导电损耗的影响。

正如在前面的例子中所看到的,栅极驱动器可以在SiC设计中发挥很大的作用,并受益于增加功能以保持电压在控制中。

UVLO(欠压锁定)

SiC FET通常用于高功率应用,需要高栅极驱动电压,不能承受波动,以免经历显着的传导损耗和热耗散。

一个解决方案叫做欠压锁定(UVLO)。UVLO是集成到IC中的功能,以禁用电路块,如果特定电压(即电源,栅极驱动器)太低。如果输入电压低于预定阈值,则UVLO电路将不会完全通过该值或禁用电路块。

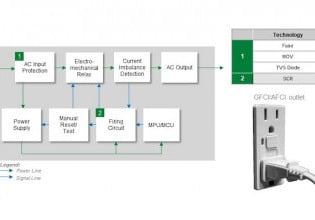

在一个UVLO例子中,输入电压被取,一个电阻分频网络被用来比较电压与参考。

示例UVLO电路块。使用的图像礼貌CTC

当R3上的电压高于参考时,比较器输出低电平,保持关闭并保持EN信号高。当该电压低于参考时,开关接通,驱动ZH低且有效地关闭以下电路块。

以这种方式,UVLO防止电路操作在不需要的电压电平,并产生更安全的电路。

UVLO是一种简单的安全预防,可配备各种IC设计。

意法半导体的新门驱动器

这个UVLO电路是焦点意法半导体最新的隔离栅极驱动IC。

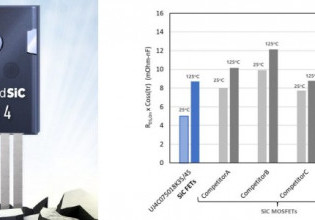

专为安全控制SiC FET而设计,stgap2sics高达1200V,可以产生高达26V的栅极驱动电压。为了提高安全性,IC增加了前几代的UVLO阈值,现在高达15.5V,因此不允许SIC由任何值降低的值驱动。

STGAP2SiCS的框图。使用的图像礼貌意法半导体

适用于工业应用,该IC可以产生最多4A的闸门驱动器,使其最大功率输出高达104W的IC。进一步的安全性来自输入和栅极驱动器之间的6kV的电流隔离。

额外的安全功能包括低功耗备用模式,硬件互锁(以防止交叉传导)和热关断保护。

随着半导体技术和其他宽带隙半导体越来越受欢迎,工程师需要不断开发方法,以确保他们的操作是有效和安全的。意法半导体公司正在用他们最新的门驱动IC来实现这一点,在一个芯片上引入UVLO和其他安全功能。