这篇技术简介解释了广泛的一些低级细节 - 我甚至可能会说普遍存在的通信界面。

相关信息

世界上有很少的电气工程师和电子爱好者在没有以某种方式与通用异步接收器/发射器(UART)接口互动。在一个技术可以很快过时的世界中,我们必须向谁创造这种简单的数字通信计划,这已经存在了几十年,并且仍然享有巨大的普及。

笔记:术语“UART”是相当模糊的。接口的各个方面——数据位数、停止位数、逻辑级别、奇偶校验——都可以适应系统的需要。在本文中,我将重点介绍现代微控制器应用程序中常见的UART实现。

能力和特征

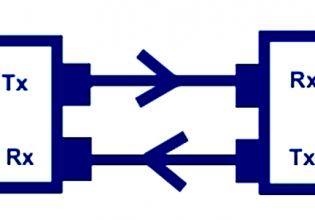

您可能知道,基本UART系统提供了具有仅三个信号的强大,中速,全双工通信:TX(传输串行数据),RX(接收串行数据)和地面。与其他协议相比,如SPI和I2C.,不需要时钟信号,因为用户提供了UART硬件所需的定时信息。

实际上,存在时钟信号,但它不是从一个通信设备传输到另一个;相反,接收器和发射机都具有内部时钟信号,该时钟信号控制如何生成改变逻辑电平(在TX侧)并解释(在RX侧)。不出所料,如果已经为不同的数据传输频率配置了发射器和接收器,则UART通信无效。而且,内部时钟信号必须是1)相对于预期频率足够精确,并且2)通过时间和温度足够稳定。

关键术语

让我们回顾一些术语,并在此过程中,我们将介绍更多UART特征:

- 开始位:一字节UART传输的第一个比特。它指示数据线正在离开其空闲状态。空闲状态通常是逻辑高的,所以起始位是逻辑低的。

- 起始位是一个开销位;这意味着它有助于接收器和发射器之间的通信,而是不转移有意义的数据。

- 停止位:一个字节UART传输的最后一点。其逻辑电平与信号的空闲状态相同,即逻辑高。这是另一个开销位。

- 波特率:可以传送数据的近似速率(以每秒位数或bps)。更精确的定义是对应于发送数字数据所需的时间(以秒)(以秒为单位)的频率(以秒为单位)。例如,通过9600波特系统,一位需要1 /(9600 bps)≈104.2μs。该系统实际上不能每秒传输9600位的有意义的数据,因为开销位需要额外的时间,并且可能在一个字节传输之间延迟。

- 奇偶校验位:一个错误检测位添加到字节的末尾。有两种类型 - “奇数奇偶校验”意味着如果数据字节包含一个,则奇偶校验位将是逻辑高的甚至逻辑高位数,“偶数奇偶校验”意味着如果数据字节包含一个,则奇偶校验位将是逻辑高的奇怪的逻辑高比特数。这可能似乎是违反直观的,但是这个想法是奇偶校验位确保逻辑高比特的数量均匀(偶数奇偶校验)或奇数(用于奇数奇偶校验)。So if you’re using even parity and the byte has three logic-high bits, the parity bit will be logic high, so that the total number of logic-high bits in the transmitted data (i.e., the byte itself plus the parity bit) is even.

- 通过强制逻辑高位的数量始终(偶数奇偶校验)或奇数(对于奇数奇偶校验),奇偶校验位提供了原油错误检测机制 - 如果有点在传输过程中稍微翻转,则of logic-high bits won’t match the chosen parity mode. Of course, the strategy breaks down if two bits are flipped, so the parity bit is far from bulletproof. If you have a serious need for error-free communication, I recommend aCRC.。

同步和采样

标准数字数据毫无意义,没有某种时钟机制。下图显示为什么:

典型的数据信号只是一种电压,其在逻辑低和逻辑高之间转换。如果它知道,接收器只能正确将这些逻辑状态转换为数字数据何时采样信号。这可以使用单独的时钟信号轻松完成 - 例如,发射机更新时钟的每个上升沿上的数据信号,然后接收器对每个下降沿上的数据进行采样。

但是,正如名称所暗示的“普遍”异步接收器/发射器“UART接口不使用时钟信号来同步TX和RX设备。那么接收器如何知道何时对发射器的数据信号进行采样?

发射机基于其时钟信号产生比特流,然后接收器的目标是使用其内部时钟信号来在每个比特周期的中间采样传入数据。在比特周期的中间进行采样不是必需的,但它是最佳的,因为更接近比特周期的开始或结束的采样使得系统对接收器和发射器之间的时钟频率差异不太稳健。

接收器序列以开始位的下降沿开始。这是在发生临界同步过程时。接收器的内部时钟与发送器的内部时钟完全独立于其他单词,该第一下降沿可以对应于接收器时钟周期中的任何点:

为了确保接收器时钟的主动边缘可以在比特周期的中间发生,发送到接收器模块的波特率时钟的频率远高于(倍数为8或16甚至32)实际的波特率。

假设一个比特周期对应16个接收机时钟周期。在这种情况下,同步和采样可以进行如下操作:

- 接收过程由起始位的下降沿启动。

- 接收机等待8个时钟周期,以便建立一个接近比特周期中间的采样点。

- 然后,接收器等待16个时钟周期,使其将其带到第一数据比特周期的中间。

- 第一个数据位被采样并存储在接收寄存器中,然后模块在采样第二数据位之前等待另一个16个时钟周期。

- 此过程重复,直到所有数据位都已采样并存储,然后止动位的上升沿返回到其空闲状态的UART接口。

结论

本文介绍了有关您可能已成功使用多次通信协议的一些细节。It is quite possible to implement a UART interface while knowing very little about the actual behavior of the signals and hardware, but a little extra knowledge—aside from the general edification that such knowledge provides—can be helpful when your UART communication isn’t working as expected.

好的文章

那么,用奇偶校验位,你只能传输7位信息吗?或者我需要重新学习grey code或者2s compliment吗?