在本视频中,我们将讨论使用运算放大器来比较一个信号的幅值和另一个信号的幅值或参考电压的电路。这些模拟比较器电路可以产生与数字组件兼容的输出信号。

运算放大器是具有差分输入级的高增益放大器。然而,大多数OP-AMP电路没有高增益并且不执行差异放大。相反,我们使用负反馈将高增益差分放大器转换为高性能和用户友好的电路,该电路放大各个地面参考信号。

在原有的高增益差分输入配置中使用该器件的唯一常见运放应用是电压比较器。电压比较器的目的是产生一个输出信号,该信号对应于运放输入端电压之间的大于或小于关系。

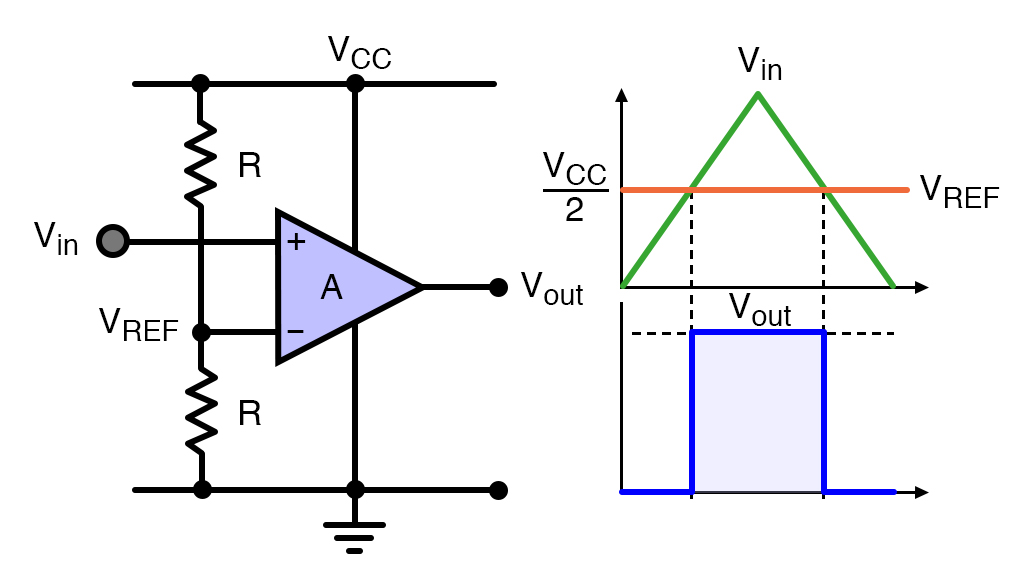

If we think of the comparator’s output as a digital signal, we can say that the comparator generates a logic high when the voltage at the non-inverting input is higher than the voltage at the inverting input and a logic low when the voltage at the non-inverting input is lower than the voltage at the inverting input.

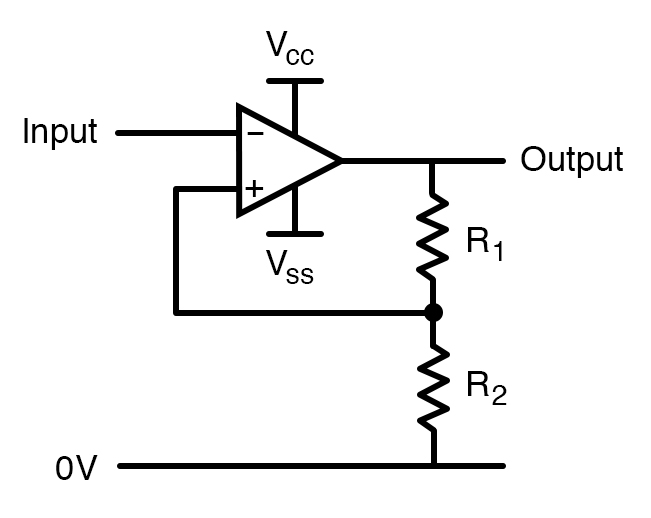

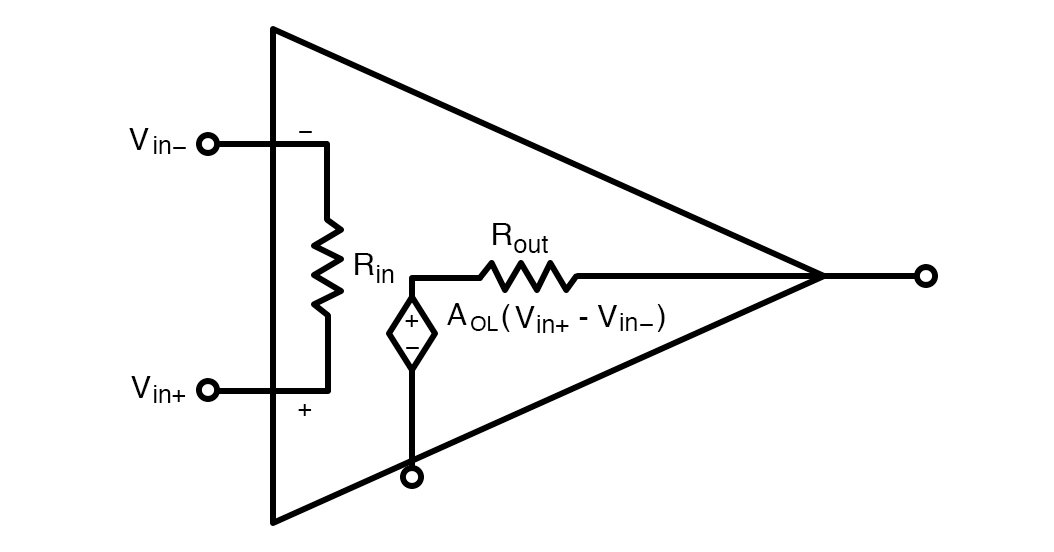

比较器运算是运放极高增益的自然结果。如图所示,充分增益(Aol.)应用于非反相输入端子处的电压与反相输入端子处的电压之间的差。

\ [V_{出}=现代{OL} \ * (V_ {+} - V_ -}{) =现代{OL} \ * V_ {DIFF} \]

因此,即使是很小的正VDIFF会导致运放输出在正电源电压或接近正电源电压时饱和,甚至一个非常小的负VDIFF将导致输出在负电源电压或接近负电源电压时饱和。如果负电源接地,比较器产生的数字信号在逻辑低电平(≈0v)和逻辑高电平(≈V)之间变化CC,这可以是3.3 V或5 V)。

虽然Op-AMPS可以用作比较器,但重要的是要理解,典型的OP-AMPS未针对这种类型的功能开环进行优化,轨到轨饱和度与基于负反馈的信号放大非常不同。如果要提高比较器电路的性能,可以使用专门作为比较器出售的放大器IC。

一种常见的比较器应用程序是产生输出信号,该信号指示输入信号是高于或低于指定的阈值电压。例如,当电源电压降至3v以下时,您可能想手动关闭电路板上的某个组件。

通过产生参考电压并使用该电压作为比较器的输入之一来实现这些类型的比较器任务。如果您需要极其精确的阈值,可以使用电压参考IC,但在许多情况下,电阻分频器足够。

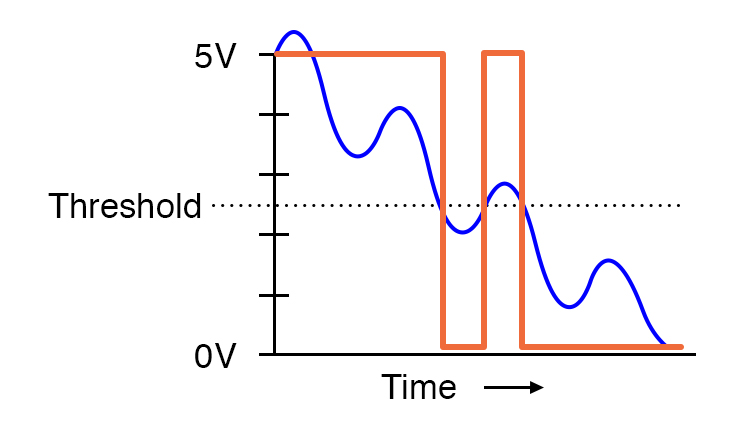

到目前为止讨论的开环比较器拓扑有一个严重的限制:噪声会导致运放在VDIFF接近0v。

例如,假设每当周期性传感器信号超过阈值电压时,微控制器需要执行一个代码块。我们将使用一个比较器来产生一个信号来启动这个代码块的执行。

然而,当传感器信号接近阈值时,小幅度、高频变化会导致信号在阈值上下快速移动。这导致VDIFF在负值和正值之间变化,进而导致多个输出转换。这些转换是不可取的,因为它们代表的是噪声行为,而不是“真实的”输入信号的行为。

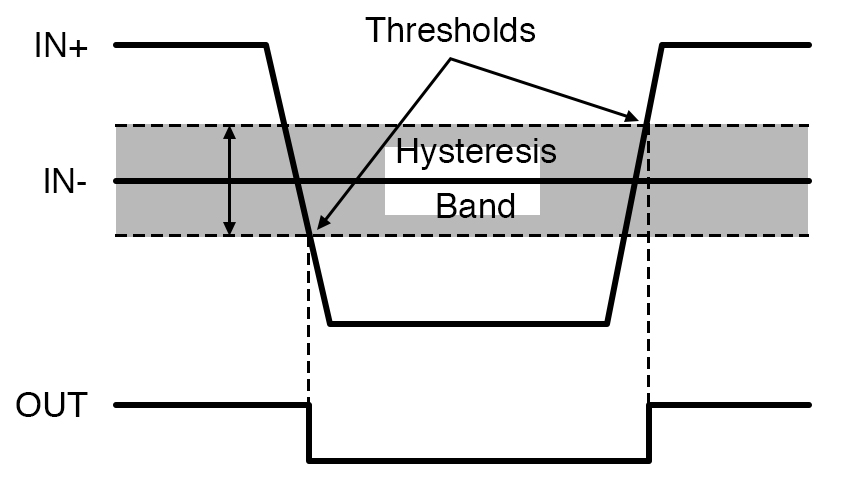

该方法解决了伪输出跃迁问题磁滞进入比较器电路。术语“滞后”是指使用不同阈值对于负对阳性过渡和正对负转换的技术。这会产生一个延伸的滞后频段,延伸到v以下DIFF= 0 V.

如下图所示,我们可以通过结合正反馈来创建不同的负对正负阈值。