| 不要只是坐在那里!构建的东西! ! |

学习分析数字电路需要学习和实践。通常,学生通过大量的实践工作示例问题与那些课本提供的检查他们的答案或老师。虽然这是好的,有一个更好的方法。

你会学到更多构建和分析实际电路,让您的测试设备提供“答案”,而不是一本书或另一个人。成功circuit-building练习,遵循这些步骤:

总是确保电源电压水平在规范您计划使用的逻辑电路。如果TTL,电源必须是一个5伏监管供给,适应值尽可能接近5.0伏直流。

一个方法你可以节省时间和减少错误的可能性逐步开始从一个非常简单的电路和添加组件增加其复杂性分析后,而不是为每个实践构建一个全新的电路问题。另一个节省时间的技巧是重用相同的组件在各种不同的电路配置。这种方式,你不需要测量任何组件的价值不止一次。

让电子本身给你答案你自己的“实践问题”!

我的经验,学生需要多练习与电路分析成为精通。为此,教师通常为学生提供大量的工作实践问题,并为学生提供答案检查自己的工作。虽然这种方法使学生精通电路理论,它未能完全教育他们。

学生不需要数学练习。他们也需要真实的,动手实践构建电路和使用的测试设备。所以,我建议以下替代方法:学生应该构建自己的“实践问题”与真正的组件,并试图预测各种逻辑状态。这种方式,数字化理论”来活着,”和学生获得实际能力他们不会获得仅仅通过求解布尔方程或简化卡诺图的地图。

这种方法的练习后的另一个原因是教学生科学的方法:测试一个假设的过程(在这种情况下,逻辑状态预测)通过执行一个真正的实验。学生也将发展真正的故障排除技巧,因为他们偶尔使电路结构错误。

花几分钟时间和你的类来回顾一些“规则”的构建电路之前就开始了。讨论这些问题和你的学生在同一个苏格拉底的方式你通常会讨论工作表的问题,而不是简单地告诉他们他们应该和不应该做什么。总是令我惊讶差学生掌握指令时呈现在一个典型的讲座(教师独白)格式!

我强烈推荐CMOS逻辑电路为家庭实验,学生可能没有访问5伏稳压电源。现代CMOS电路更崎岖的关于静电放电比第一个CMOS电路,所以担心学生伤害这些设备没有一个“正确的”实验室设立在家里都是没有必要的。

写给那些教练可能会抱怨“浪费”时间需要学生建立真正的电路,而不只是数学分析理论电路:

你的课程学生的目的是什么?

如果你的学生将与实际电路,然后他们应该学习尽可能在实际电路。如果你的目标是教育理论物理学家,那么坚持抽象分析,通过各种方法!但是我们大多数人计划为我们的学生做一些在现实世界中与我们给他们的教育。beplay网页版本“浪费”时间建立真实电路将支付巨额红利的时候为他们将他们的知识应用到实际问题。

此外,让学生建立自己的练习教他们如何执行的问题主要研究,从而让他们继续他们的电气/电子自主教育。beplay网页版本

在大多数科学、现实的实验更加困难和昂贵的比电路设置。核物理学、生物学、地质学和化学教授就希望能够有学生高等数学应用到实际实验带来不安全隐患和花费不到一本教科书。他们不能,但你能。你的科学利用固有的便利,得到你的这些学生练习他们的数学很多真正的电路!

常见的直粱功率变换器电路拓扑结构使用的一对晶体管开关直流电流通过升压变压器的中心抽头绕组,像这样:

|

|

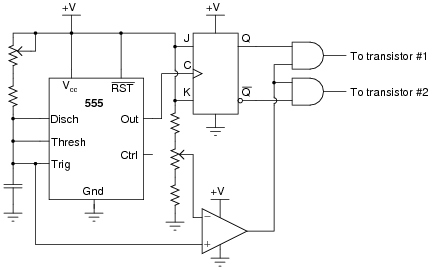

为了使这种形式的电路正常工作,晶体管“解雇”必须精确地同步信号来确保这两个永远不会同时开启。下面的示意图显示了一个电路生成必要的信号:

|

|

解释这个电路是如何工作的,并确定频率的位置控制和脉冲频宽比控制电位器。

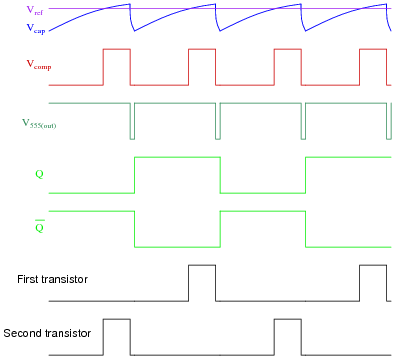

一个计时图抵得上一千字:

|

|

|

|

后续的问题:你会哪个方向移动频率电位器来增加电路的输出频率?哪个方向你会把责任周期电位计增加吗?

挑战的问题:假设你是原型电路没有示波器。你怎么能测试电路,以确保最终的输出脉冲的晶体管同时从未“高”逻辑状态?假设您有一个零件分类包括发光二极管和其它无源元件。

这个问题是一个运动原理图和时序图解释。顺便说一下,我已经建成并测试了这条赛道,我可以说它工作得很好。

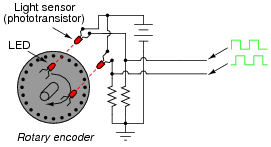

常见的一种旋转编码器是建立生产交输出:

|

|

两个领导/光电晶体管对被安排在这样一种方式,其脉冲输出总是90o彼此的阶段。正交输出编码器是有用的,因为他们允许我们确定运动方向以及增量位置。

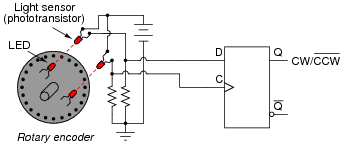

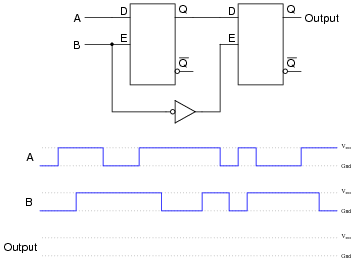

建立一个正交方向探测器电路很容易,如果你使用d型触发器:

|

|

分析电路,并解释它是如何工作的。

这个电路的操作相当容易理解如果你画的脉搏图,分析了触发器的输出。当编码器圆盘旋转顺时针,Q输出高;当逆时针,问就低。

后续问题:评论符号用于此电路的输出。什么标签“CW /(公约)”告诉你,不用分析电路吗?

交这样的定向电路变得很重要当编码器与数字计数器电路。补充符号在计数器电路也很常见。

学生可能表现出不愿画一个计时图解决这个问题时,即使当他们意识到这样一个图的实用程序。相反,许多人将试图找出电路只要看它。注意强调“试一试。”This circuit is much more difficult to figure out without a timing diagram! Withhold your explanation of this circuit until each student shows you a timing diagram for it. Emphasize the fact that this step, although it consumes a bit of time, is actually a time-saver in the end.

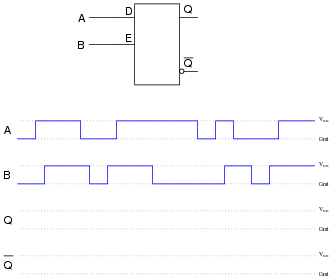

确定最终的输出以下电路状态随着时间的推移,由d型封闭的门闩:

|

|

具体什么时候在脉冲图最终的输出假设输入的状态吗?这种行为是如何不同于正常反应型锁?

|

|

最终的输出假设相同的逻辑状态作为输入时,才使输入信号(B)转换从“高”“低”。

注意,通过添加另一个门闩,整体行为仅略像d型锁的行为。通过添加第二个门闩,我们改变了此电路触发器的,特别是主-从品种。

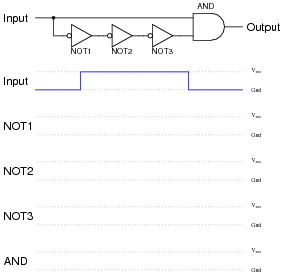

通常,传播延迟是一个不受欢迎的逻辑门的特点,我们只需要住在一起。其他时候,它是有用的,甚至是必要的特征。以电路为例:

|

|

如果盖茨构成电路零传播延迟,它会执行任何有用的功能。来验证这个可悲的事实,分析其稳态响应“低”输入信号,然后一个“高”的输入信号。什么状态与门的输出总是在吗?

现在,考虑传播延迟完成时间图的分析对于每个门的输出,输入信号转换从低到高,再由高到低:

|

|

你注意到现在的状态和门的输出?

|

|

后续问题:描述什么是必要的条件获得一个“高”从该电路的输出信号,而决定这个“高”脉冲的持续时间。

告诉你的学生这个电路是一种特殊类型的只有一次的,输出一个脉冲持续时间有限,对于每一个输入信号的前沿过渡。

问问你的学生我们会做的,如果我们想使输出脉冲的一次性电路长(或更短)。

解释如何使用示波器测量半导体逻辑门的传播延迟。画一个示意图,如果必要的。是传播延迟时间通常为数字等于门从“高”“低”转变,从“高”与“低”?参考数据来证明你beplay无法取钱的答案。

另外,是否发表评论机电式继电器有一个等效参数来传播延迟。如果是这样,你怎么想传递的延迟的大小比较的半导体门,为什么?

我将离开你的实验设计细节。然而,我将告诉你,你不一定要用数字存储示波器“捕捉”瞬态波形测量传播延迟,如果你申请一个小创意。提示:使用高频方波信号发生器发送你选择的门,并使用非存储示波器监视结果。

是的,机电继电器也有内在的延迟时间,这往往是远比那些遇到半导体逻辑门。

这个问题是一个优秀的课堂演示。它显示了这个实用参数而言学生应该能够kinesthetically与。

你的学生对研究数据负责,而不是仅仅查找教科书中的信息。beplay无法取钱最终,阅读笔记写的数据和应用程序的制造商beplay无法取钱将会让他们跟上最新技术比教科书更有效,因为大多数教科书我看过往往落后于先进的几年至少。有丰富的信息获得制造商的文学,所以准备你的学生使用它!

向学生解释,继电器驱动不仅延迟,但他们中的大多数也表现出显著的联系反弹。联系反弹问题尤其是在继电器信号发送到固态逻辑电路,在更大的程度上比其他继电器,继电器发出信号。专用继电器可以获得的设计减少动作时间和反弹,但特征远比任何等效影响半导体逻辑门。

Determine Q 和 [Q] 输出 状态 的 D-type 封闭 latch, conditions: 给 下面 的 输入

|

|

现在,假设我们添加一个propagation-delay-based一次性电路使线的d型封闭的门闩。Re-analyze电路的输出,因为相同的输入条件:

|

|

评论这两个电路之间的差异的反应,尤其是使输入信号(B)的引用。

|

|

|

|

后续的问题:这些电路称为之一边沿触发。它是哪一个?

挑战的问题:在现实中,输出波形为这些场景将会动摇,由于组成盖茨内的传播延迟。:真正的输出,占这些延迟。

与你的学生讨论edge-triggering的概念,以及它如何实现(之一)的电路问题。请他们描述任何提示他们可能发现分析脉冲波形。具体地说,是在任何特定的情况下,我们需要密切关注D输入信号来确定输出做什么,和任何时间,我们可以忽略D输入状态?

挑战问题传播延迟是为了提醒学生,完美同步时序图出现在教科书并不完全在现实生活中会发生什么。问你的学生详细说明现实的条件会让这样的传播延迟有关。有数字电路的应用,我们几乎可以忽略这样的延误?

这里显示是两个数字组件:一个d型门闩和一个型触发器:

|

|

除了愚蠢的名字,“触发器”从一个门闩的区别是什么?怎么这两个电路的功能有何不同?

“触发器”是一个门闩,改变输出只有在上升或下降边缘时钟脉冲。

注意到您的学生的时间输入一个触发器被称为时钟而不是一个启用。让他们确定什么象征意义的差异显示这两个设备之间的区别。

解释如何添加propagation-delay-based一次性电路使输入的因此门闩改变它的行为:

|

|

具体来说,参考你的回答真值表的电路。

这个设备可以改变状态的输出只有当“时钟”信号(C)是过渡从低到高:

|

|

挑战的问题:究竟发生在这个因此触发器的“无效”状态?

讨论和你的学生发生了什么在这个电路时钟信号时做任何事除了过渡从低到高。什么条件(s)是等价的在一个常规因此封闭锁电路?

挑战尤其难以回答的问题。“无效”国家很容易确定在常规因此锁存器电路,封闭或un-gated。然而,由于一个因此触发器只是暂时“封闭的”边缘的时钟信号,美国的产出下降到边缘事件已经过去后更加难以确定。

平原因此锁电路是“套”通过激活输入和取消R S输入。相反,它们是“重置”通过激活R输入和取消年代输入。封闭的门闩和拖鞋,然而,是一个小更复杂:

|

|

描述输入条件必须迫使这些多谐振荡器电路集和重置。

因此封闭锁:

因此触发器:

因此封闭锁:

因此触发器:

这个问题的目的是审查的定义“组”和“重置”,以及区分门闩和人字拖。

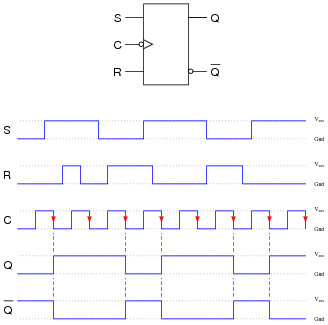

确定这个因此触发器的输出状态,由于脉冲输入如图所示:

|

|

|

|

为了成功地回答这个问题,学生必须确定的“泡沫”意味着时钟输入,和与时间图。问问你的学生共享任何提示他们可能关于时序图的分析,具体什么点在图中是至关重要的(即什么时间点是唯一点的输出可能会改变状态)。

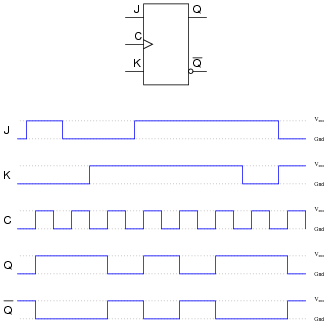

一个非常受欢迎的变化因此触发器是所谓的主题j - k触发器电路如图所示:

|

|

注意,一个因此触发器变成了j - k触发器通过添加另一层的输出反馈回使NAND盖茨(现在三个输入,而不是两个输入)。这添加反馈完成什么呢?表达你的回答真值表的形式。

一种考虑反馈线回到第一个逻辑门是把它们看作是额外的启用lines, Q 和 [Q] 输出 选择性 地 启用 只是 其中 的 一 个 NAND 盖茨 一 个 时候

确定必要的设置,输入条件重置,切换这两个j - k拖鞋:

|

|

高电平输入的j - k触发器:

校验输入的j - k触发器:

在要么情况下,您使触发器进入这三个模式通过以下几点:

不过,确切地说,这就是你需要做的每一个触发器,所述的“高”和“低”逻辑状态:

高电平输入的j - k触发器:

校验输入的j - k触发器:

这个问题综述了j - k拖鞋的基本模式,以及校验输入的重要性。

确定这个j - k触发器的输出状态,由于脉冲输入如图所示:

|

|

|

|

让学生来识别这些地区在触发器被计时图上集,重置,连接。

确定这个D触发器的输出状态,由于脉冲输入如图所示:

|

|

|

|

让学生来识别这些地区在触发器被计时图上集和重置。

确定这个j - k触发器的输出状态,由于脉冲输入如图所示:

|

|

|

|

让学生来识别这些地区在触发器被计时图上集,重置,连接。

拖鞋通常都配备了异步输入行以及同步输入行。这个j - k触发器,例如,“预设”和“明确”异步输入:

|

|

描述这些输入的功能。为什么我们想要在一个电路中使用它们吗?解释什么是“同步”的输入,以及为什么他们指定的这一项。

另外,请注意,这两个异步输入校验。通常,异步输入几乎总是校验而不是高电平,即使所有的其他输入高电平触发。你认为这是为什么?

“异步”输入力输出的“套”或“重置”国家独立的时钟。“同步”输入控制触发器的输出只有在时钟脉冲。

至于为什么异步输入校验,我不会直接给你答案。但我将给你一个提示:考虑TTL这个触发器的实现。

注意你的学生,有时预设和明确的输入被称为直接设置和直接复位,分别。检查与你的学生是什么意思“校验”与“高电平输入。”Ask them what consequences might arise if a circuit designer misunderstood the input states and failed to provide the right type of signal to the circuit.

一个科学家使用微处理器系统监控布尔(“高”或“低”)一个粒子的状态传感器在高速核的实验。问题是,传感器检测到的核事件来来去去快得多微处理器能够样本。简单地说,脉冲输出的传感器太短暂的“捕获”的微处理器每次:

|

|

她问几个技术人员来解决这个问题。一个试图改变微处理器的程序实现更快的抽样评定等级,都无济于事。另一个粒子重新校准传感器反应慢,但这只会导致错过了数据(因为现实世界数据不相应慢下来!)。无解的尝试工作到目前为止,因为微处理器的根本问题是太缓慢“捕获”极短脉冲事件来自粒子传感器。需要的是某种形式的外部电路在“读”传感器的状态采样脉冲的前沿,然后认为数字足够可靠的微处理器状态寄存器。

最后,另一个电子技术员提出这个解决方案时,然后去度假,让你实现它:

|

|

解释这个d型触发器的工作原理来解决这个问题,和微处理器必须采取什么行动销使触发器的输出函数作为多个脉冲探测器。

触发器成为“套”每一次脉冲来自传感器。微处理器必须明确阅读后触发器捕获脉冲,因此触发器将准备捕获和保存一个新的脉冲。

挑战的问题:你会推荐使用什么逻辑的触发器对于这个应用程序,考虑到需要极快的反应?不要只是说“TTL,”。研究当前最快的现代逻辑家庭制造!

这是一个非常实际应用d型触发器,并介绍一个基于微处理器的数据采集系统的缺陷。向学生解释,一个微处理器所需的有限时间周期通过其程序可能导致这样的状况实时事件在哪里错过因为微处理器是“忙碌”做其他事情。

确定至少一个组件故障将导致触发器表明“顺时针”,不管编码器运动:

|

|

为每个提出缺点,解释为什么这将导致描述问题。

后续问题:解释为什么光电晶体管附近的环境光的存在也可能导致这个问题的发生。

一定要与你的学生讨论他们提出错误的原因会导致陈述的问题。

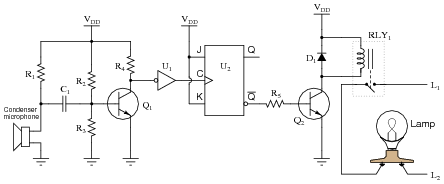

假设一个学生想要建造一个声控灯控制电路,即一个鼓掌或其他大声的噪音把灯,和另一个单拍。声探测和lamp-drive电路如图所示:

|

|

这个原理图添加一个j - k触发器实现切换功能。

|

|

Some 学生 可能 会 问 是否 有 意义 使用 [Q] 输出 而 不是 Q. Discuss 这 与 students: 他们 是否 认为 这 将 使 任何 difference, 或 如果 它 只是 一 个 任意 的 选择 由 circuit’s designer.然后,问他们他们会如何证明他们的判断。

有很多“如果”失败场景你可以问你的学生,挑战他们分析这个电路故障诊断的视角。如果时间允许,找点乐子。

If 时钟 频率 驱动 这个 触发器 是 240 Hz, flip-flop’s 输出 信号 的 频率 是 什么 (either Q 或 [Q])?

|

|

f出= 120赫兹

后续的问题:你怎么能使用另一个触发器获得60 Hz的方波信号从这个电路?

问问你的学生认为这种类型的电路的一些实际应用。对于那些在音乐上斜,问他们什么音乐音符的频率之间的关系是一个精确的2:1比例(提示:这是相同的时间间隔八白色钢琴键盘上的键)。这样一个电路怎么可能被用在一个音乐合成器吗?

这里显示的触发器电路划分为同步因为两人字拖接收时钟脉冲在同一时间:

|

|

定义以下参数:

然后,说明这些参数相关的所示的电路中。

时钟频率必须足够缓慢,足够了安装时间之前下一个时钟脉冲。的传播延迟时间FF1也必须大于保存时间FF2。当然,时钟信号的脉冲宽度必须足够两人字拖可靠的“时钟”。

我可以简单地要求学生定义条款,但在哪里有趣?不过,说真的,这些概念将更多的意义学生当他们从一个实际的上下文。毕竟,整个教学这些概念的目的是学生能够应用他们,对吗?

定位一个触发器集成电路制造商的数据表,并研究以下参数:

我会让你做研究这个问题!

以防学生声称他们“找不到任何部分的研究,建议如下:

虽然切换j - k触发器的功能是一个最受欢迎的用途,这不是唯一类型的触发器执行切换函数的能力。看配置的令人惊讶的是通用的d型触发器来做同样的事情:

|

|

解释这个电路执行相关的“切换”功能更常见的j - k拖鞋。

At 每个 时钟 pulse, 触发器 必须 切换 到 相反 的 状态 因为 D 接收 从 [Q]. 倒 反馈

这个问题的主要目的是让学生看到切换不是j - k拖鞋的专属领域。这个事实也许会特别有用如果你需要一个切换功能的电路,但只有一个可用的d型触发器,不是一个j - k触发器。

一个学生有想法做一个J - K触发器切换:为什么不把J, K,一起和时钟输入,把他们所有相同的方波脉冲?如果输入高电平和时钟是正的边沿触发,J和K的输入都应该“高”在同一时刻时钟信号转换从低到高,因此建立切换的必要条件(J = 1, K = 1,时钟转换):

|

|

不幸的是,j - k触发器拒绝当这个切换电路。No 物质 多少 时钟 脉冲 receives, Q 和 [Q] 输出 保持 在 原来 的 州 —— 触发器 仍然 “latched.“解释学生的触发器电路的实际原因想法不会工作。

与所有输入捆绑在一起,零设置时间在前的J和K输入时钟脉冲上升。

这个问题的目的是让学生考虑设置时间,并看到它的重要性通过提供一个场景,电路不工作,因为一直在忽略此参数。

预测这个声音控制灯电路的操作会影响以下错误的结果。考虑每个故障独立(即一次,没有多个错误):

|

|

对于每个这些条件,解释为什么由此产生的影响将发生。

这个问题的目的是接近的电路故障诊断领域的角度认识错误是什么,而不是只知道症状是什么。虽然这并不一定是现实的角度来看,它可以帮助学生建立诊断所必需的基础知识从经验数据断电路。这样的问题应遵循(最终)由其他问题让学生识别可能基于测量的缺点。

的条款和条件下出版知识共享归因执照